|

|

|

|

RISC-V

RISC-V is a free and open ISA (instruction set architecture) that provides an alternative to the closed ISAs used in today's x86 and ARM processors. RISC-V is already widely used in microcontrollers and other devices with embedded CPU cores, such as SSD controllers. Right now, however, RISC-V is still developmental as an end-user and server technology. This said, very rapid progress is being made, with a wide range of end user computing activities already possible on RISC-V hardware. This web page provides an introduction to RISC-V, and is continually updated to relfect key developments. You can also learn more in the following ExplainingComputers videos:

Note that there will be a new RISC-V Update video posted in the first quarter of 2024. CLOSED & OPEN ISAs

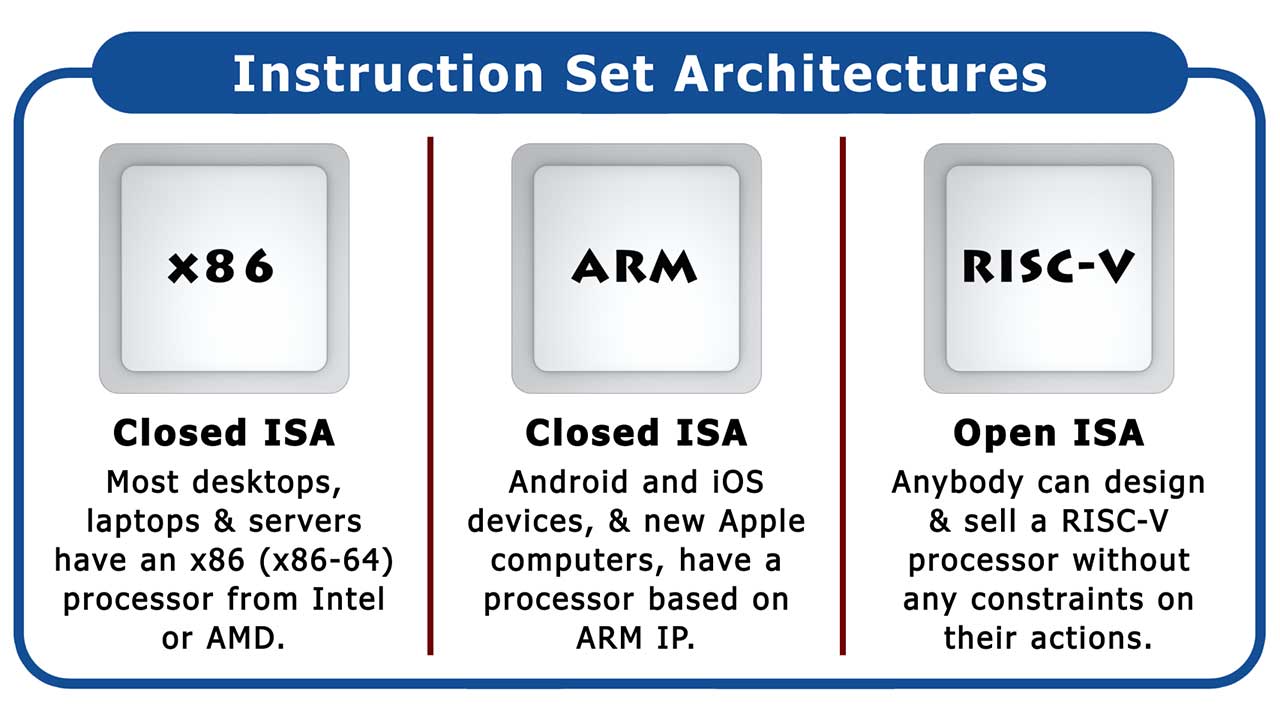

Today, as shown in the above diagram, practically all computers are based on one of two closed instruction set architectures. The first of these is x86, or technically x86-64, with most desktops, laptops and servers having an x86 processor from Intel or AMD. The x86 ISA was created by Intel, and then extended into its current 64-bit incarnation by AMD, with the two companies having licensing agreements that allow both of them to design and sell x86 CPUs. Alongside x86, todays other dominant ISA is ARM, with practically all Android and iOS devices, and new Apple computers, having a processor based on ARM intellectual property. Many different companies design and manufacture ARM processors, but because the ARM ISA is closed, they all have to pay licence fees to ARM Limited, which hence maintains control of its technology. In contrast, the RISC-V ISA is free and open. This means that anybody can design and sell a RISC-V processor core without any constraints on their actions. The designs for RISC-V cores may then be used in the design of microcontrollers, CPUs, systems on a chip, or other components, which may in turn be manufactured in a fabrication plant. Whilst the RISC-V ISA is free and open, it’s up to the designers of RISC-V cores and chips to decide whether the intellectual property they have created will be placed in the public domain. This means that not all RISC-V technology is open hardware, with some RISC-V core and chip designs being open, and some being closed. In addition to having no intellectual property restrictions, the RISC-V ISA can also be freely extended. New instructions are added via a custom ISA extension which does not break compatibility with the main RISC-V specification. This gives designers great flexibility to incorporate new instructions for their particular applications, which can be particularly liberating when creating custom processors for use in cars, robots, and a wide range of other industrial and consumer products. INTERTITLE: RISC-V ORIGINSRISC stands for "reduced instruction set computing", and describes a processor architecture that executes a large number of simple instructions to complete a task. An alternative to RISC is CISC, which stands for "complex instruction set computing", and executes a smaller number of more complex instructions to complete a processing activity. Today, the difference between RISC and CISC is more blurry than it used to be. But we may still reasonably describe the x86 ISA as CISC, and the ARM ISA as RISC. So what about RISC-V? Well, RISC-V is a specific RISC processor architecture whose development commenced in May 2010 in the Parallel Computing Laboratory at the University of California Berkeley. One of the first ever RISC architectures was created at Berkeley between 1980 and 1984, with RISC-V getting its name because it is the fifth generation of Berkeley RISC. RISC-V was initially created to support research and education, with the first RISC-V Instruction Set Manual published as an open source document in May 2011.

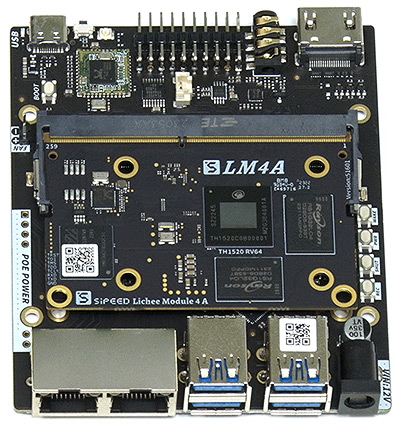

RISC-V INTERNATIONALTo make it possible for RISC-V to be used in industry, in 2015 a non-profit governing body was established to maintain and support its open standards. This organization was initially called the RISC-V Foundation and was based in the United States. However, due to concerns relating to the potential impact of future US trade regulations, in 2020 RISC-V’s governing body relocated to Switzerland and became RISC-V International. RISC-V International describes itself as "the global non-profit home of the open standard RISC-V Instruction Set Architecture (ISA), related specifications, and stakeholder community". And already it has over 3,800 members from 70 countries -- more than double the number of members it had in early 2022. Premiere members include large computing industry players like Google, Intel, Alibaba, Qualcom and Huawei, as well as RISC-V pionners such as SiFive (which was set up by the Berkeley team that designed the RISC-V ISA). Other RISC-V International members include AMD, Western Digital, Samsung, Seagate and Sony. RISC-V APPLICATION & DEVELOPMENTRISC-V is already firmly established as an embedded microprocessor technology, with RISC-V cores now commonly included in storage controllers, camera modules and other components and devices. Reflecting this, as revealed in this keynote video, Qualcomm has already shipped 650 million embedded RISC-V cores. And in July 2022, RISC-V International reported that over 10 billion cores have now shipped. In September 2022, it was also announced that NASA has selected RISC-V cores for its next generation High-Performance Spaceflight Computing (HPSC) processor. And in early 2023, it was reported that Google wants RISC-V to be a Tier-1 Android Architecture. 2023 was also the year that RISC-V single board computers able to credibly run a desktop Linux distro started to become available, and for a realistic price. Whilst all such products are all currently development boards -- and absolutely NOT end-user or consumer products -- they have already demonstrated that RISC-V is becoming a credible desktop computing architecture. Indeed, as demonstrated in the ExplainingComputers RISC-V Week video, it already possible to do the majority of everyday desktop computing activities on RISC-V hardware. It there therefore reasonable to predict that end-user RISC-V mini PCs and tablets will arrive on the market within the next few years. You can see reviews and demos of current RISC-V single board computers in these videos:

Beyond the worlds of embedded and end user computing, RISC-V is also headed for data center application. For example, pioneer Ventana has already announced a family of data center RISC-V CPUs known as Veyron. Meanwhile, Tenstorrent is also developing a high-performance server and AI RISC-V processor called Ascalon. |

RISC-V is a free and open ISA that provides an alternative to the closed ISAs used in today's x86 and ARM processors. |

|

| ||